| 您现在的位置:首页 > 技术资料 |

|

高速ADC的低抖动时钟设计

引言 ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。在A/D转换过程中引入的噪声来源较多,主要包括热噪声、ADC电源的纹波、参考电平的纹波、采样时钟抖动引起的相位噪声以及量化错误引起的噪声等。除由量化错误引入的噪声不可避免外,可以采取许多措施以减小到达ADC前的噪声功率,如采用噪声性能较好的放大器、合理的电路布局、合理设计采样时钟产生电路、合理设计ADC的供电以及采用退耦电容等。本文主要讨论采样时钟抖动对ADC信噪比性能的影响以及低抖动采样时钟电路的设计。

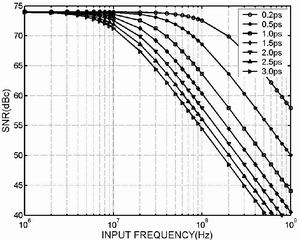

(a)12位ADC理想信噪比

(b)AD9245实测信噪比 图1 不同时钟抖动情形下12位ADC的信噪比示意图 时钟抖动对ADC

采样时钟的抖动是一个短期的、非积累性变量,表示数字信号的实际定时位置与其理想位置的时间偏差。时钟源产生的抖动会使ADC的内部电路错误地触发采样时间,结果造成模拟输入信号在幅度上的误采样,从而恶化ADC的信噪比。

由图1可以看出时钟的抖动对ADC信噪比性能的恶化影响是十分明显的,相同时种抖动情形下进入到ADC的信号频率越高,其性能恶化就越大,同一输入信号频率情形下,采样时钟抖动越大,则ADC信噪比性能恶化也越大。对比图1中两个示意图可以看出实测的采样时钟抖动对ADC信噪比性能的影响同理论分析得到的结果是十分吻合的,这也证明了理论分析的正确性。因此,在实际应用时不能完全依据理想的信噪比公式来选择A/D转换芯片,而应该参考芯片制造商给出的实测性能曲线和所设计的采样时钟的抖动性能来合理选择适合设计需要的A/D转换芯片,并留出一定的设计裕量。

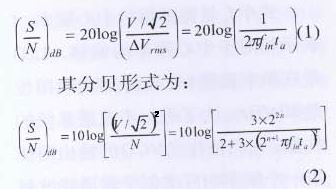

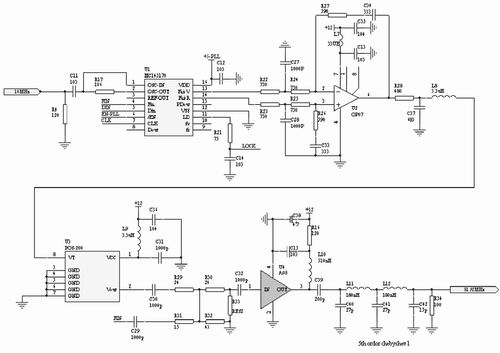

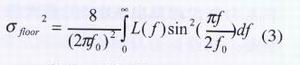

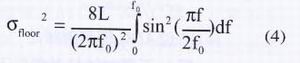

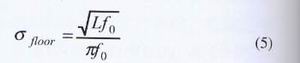

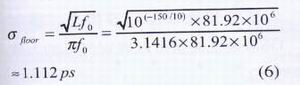

图2 一个实用的低抖动时钟产生电路 两种实用的低抖动采样时钟产生电路 直接测量时钟抖动是比较困难的,一般采用间接测量的方法,为此本节首先给出时钟抖动的产生机制。时钟抖动是由时钟产生电路(一般是基于低相位噪声压控振荡器的锁相环路)内部各种噪声源所引起的,例如热噪声(主要是压控振荡器输出信号的热噪声基底)、相位噪声和杂散噪声等,理论分析表明:当所需产生的频率较高时,相位噪声和杂散噪声对时钟抖动的恶化并不明显。 一般来说,VCO输出级放大器的热噪声基底可以看成有限带宽的高斯白噪声,其有效带宽大约为工作频率的两倍。当VCO正确地调谐到需要的输出频率时,噪声基底对抖动的影响可以用下面的公式计算:

理论上可以认为从锁相环路输出信号的相位噪声特性同VCO特性基本一致,但实际的锁相电路会引入一定的噪声,而VCO输出放大器也会使产生的时钟信号的相位噪声特性变差。所以在进行锁相环电路的设计时,除了选择具有较低相位噪声的VCO外,还应选择具有较低噪声系数的放大器或时钟缓冲器,并尽量将时钟产生电路与其它电路分隔开来。 基于低相位噪声VCO的可变采样时钟 图2给出了一个实用的基于低相位噪声VCO的低抖动可变采样时钟产生电路。 图2中以MC145170作为时钟产生环路的频率合成器,选用Mini-Circuits公司的低相位噪声压控振荡器POS-200作为

基于极低相位噪声温度补偿晶振的非可变采样时钟 在确定采样频率后,如果并不要求时钟产生电路产生的时钟可变的话,就可采用基于温度补偿晶振的时钟产生方法。首先由公式(2)根据所需的ADC信噪比确定最大容许的时钟抖动,然后由公式(5)反推出最大容忍的相位噪声基底,最后给出不同频率偏差点上的相位噪声特性并交由晶振制作工厂定制即可。这是一种最简单的时种产生方法,基本不需要作太多调试,但它只适合固定时钟采样的情况。 在利用上述两种方法产生采样时钟时,一个值得注意的地方就是采样时钟电路应尽可能与存在噪声的数字系统独立开来,在采样时钟的通路中也不应该有逻辑门电路,一般来说,一个逻辑门将会产生几个皮秒甚至十几皮秒的定时抖动。在设计时应该把采样时钟产生电路和系统的数字及模拟部分分离。 结语 本文首先分析了采样时钟抖动对ADC信噪比性能的影响,然后指出产生时种抖动的原因,最后给出了两种实用的采样时钟产生方案:基于低相位噪声VCO的可变采样时钟及基于极低相位噪声温度补偿晶振的非可变采样时钟的产生方法。

| ||||||||||||||||